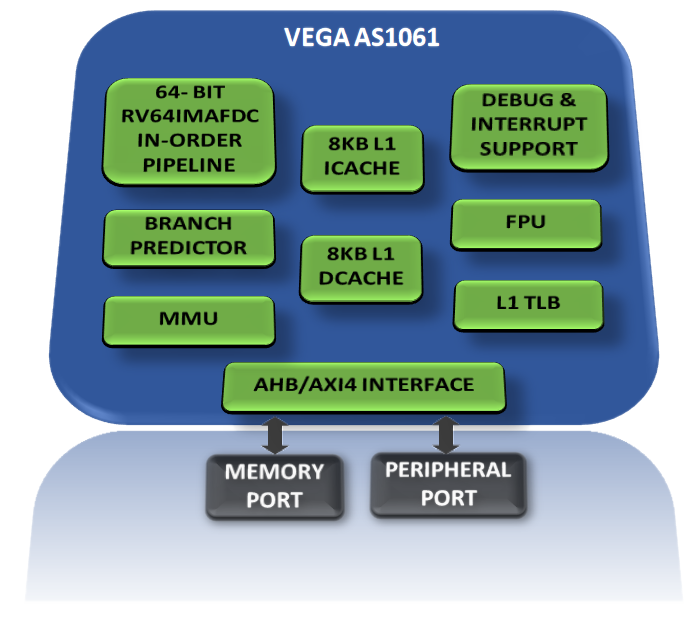

VEGA AS1061 is a 64-bit CPU IP core based on RISC-V Instruction Set Architecture. It is capable of delivering high performance with support for single and double precision floating point instructions, and MMU for Linux based applications. AS 1061 with a 6-stage pipeline comes with branch prediction for efficient branch execution, and Instruction and Data caches. Features include PLIC and vectored interrupts for serving various types of system events. An AXI or AHB standard interface enables ease of system integration and a JTAG interface is provided for debug support.

Key features

- RISC-V 64GC (RV64IMAFDC) Instruction Set Architecture

- 6 stage in-order pipeline implementation

- 16/32-bit mix instruction format for better code density

- Branch predictor: BTB, BHT, RAS

- Optional Memory Management Unit (MMU) and Physical Memory Protection (PMP)

- Harvard architecture (separate instruction and data buses)

- Supports user, supervisor and machine mode privilege levels.

- High-performance multiply/divide unit

- Configurable AXI4 or AHB external interface

- Configurable, L1 caches

- 8 KiB L1 I-cache (Typical)

- 8 KiB L1 D-cache (Typical)

- Platform Level Interrupt Controller

- Up to 127 IRQs

- Low interrupt latency

- Vectored interrupt support

- Advanced Integrated Debug Controller

- JTAG compliant interface

- HW/SW breakpoints support

- Debug extension allowing Eclipse debugging via a GDB >> openOCD >> JTAG connection

- Linux compatible

- Zephyr compatible

- FreeRTOS port

- High-performance embedded

- Consumer Electronics

- Motor Control

- Industrial Automation

- Storage